【Verilog学习】-10-时序逻辑-移位寄存器

Shift4

question

Build a 4-bit shift register (right shift), with asynchronous reset, synchronous load, and enable.

areset: Resets shift register to zero.load: Loads shift register withdata[3:0]instead of shifting.ena: Shift right (q[3]becomes zero,q[0]is shifted out and disappears).q: The contents of the shift register.

If both the load and ena inputs are asserted (1), the load input has higher priority.

Module Declaration

1 | module top_module( |

solution

1 | // my answer |

Rotate100

question

Build a 100-bit left/right rotator, with synchronous load and left/right enable. A rotator shifts-in the shifted-out bit from the other end of the register, unlike a shifter that discards the shifted-out bit and shifts in a zero. If enabled, a rotator rotates the bits around and does not modify/discard them.

load: Loads shift register withdata[99:0]instead of rotating.ena[1:0]

: Chooses whether and which direction to rotate.

2'b01rotates right by one bit2'b10rotates left by one bit2'b00and2'b11do not rotate.

q: The contents of the rotator.

Module Declaration

1 | module top_module( |

solution

1 | // my ans |

debug

- case 里面对应的一个情况超过了一个语句描述,则需要用begin end

Shift18-Arithmetic Shift Register

question

Build a 64-bit arithmetic shift register, with synchronous load. The shifter can shift both left and right, and by 1 or 8 bit positions, selected by amount.

An arithmetic right shift shifts in the sign bit of the number in the shift register (q[63] in this case) instead of zero as done by a logical right shift. Another way of thinking about an arithmetic right shift is that it assumes the number being shifted is signed and preserves the sign, so that arithmetic right shift divides a signed number by a power of two.

There is no difference between logical and arithmetic left shifts.

load: Loads shift register withdata[63:0]instead of shifting.ena: Chooses whether to shift.amount

: Chooses which direction and how much to shift.

2'b00: shift left by 1 bit.2'b01: shift left by 8 bits.2'b10: shift right by 1 bit.2'b11: shift right by 8 bits.

q: The contents of the shifter.

Module Declaration

1 | module top_module( |

Hint…

A 5-bit number 11000 arithmetic right-shifted by 1 is 11100, while a logical right shift would produce 01100.

Similarly, a 5-bit number 01000 arithmetic right-shifted by 1 is 00100, and a logical right shift would produce the same result, because the original number was non-negative.

solution

1 | module top_module( |

debug

- 三元运算符语法错误:正确:

q <= q[63] ? {1'b1,q[63:1]} : {1'b0,q[63:1]};;错误:q[63] ? q <= {1'b1,q[63:1]} : q <= {1'b0,q[63:1]}; - case 的对象错误:R:amount;E:ena。

- case 的参数错误:R:2’b10;E:10。

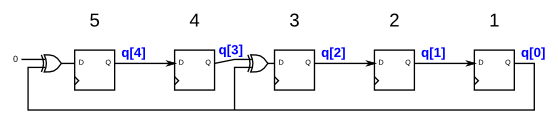

LFSR

A linear feedback shift register is a shift register usually with a few XOR gates to produce the next state of the shift register. A Galois LFSR is one particular arrangement where bit positions with a “tap” are XORed with the output bit to produce its next value, while bit positions without a tap shift. If the taps positions are carefully chosen, the LFSR can be made to be “maximum-length”. A maximum-length LFSR of n bits cycles through 2n-1 states before repeating (the all-zero state is never reached).

The following diagram shows a 5-bit maximal-length Galois LFSR with taps at bit positions 5 and 3. (Tap positions are usually numbered starting from 1). Note that I drew the XOR gate at position 5 for consistency, but one of the XOR gate inputs is 0.

Build this LFSR. The reset should reset the LFSR to 1.

Module Declaration

1 | module top_module( |

Hint…

The first few states starting at 1 are 00001, 10100, 01010, 00101, … The LFSR should cycle through 31 states before returning to 00001.

solution

1 | // my answer |

summary

这里的作者使用了状态机的写法,通过组合逻辑列出其下一状态的值,这里需要注意的是,组合逻辑使用的是阻塞赋值,后一个值将前一个值覆盖,电路里将直接忽略前一个时刻的值。

Mt2015 lfsr

question

Taken from 2015 midterm question 5. See also the first part of this question: mt2015_muxdff

Write the Verilog code for this sequential circuit (Submodules are ok, but the top-level must be named top_module). Assume that you are going to implement the circuit on the DE1-SoC board. Connect the R inputs to the SW switches, connect Clock to KEY[0], and L to KEY[1]. Connect the Q outputs to the red lights LEDR.

Module Declaration

1 | module top_module ( |

Hint…

This circuit is an example of a Linear Feedback Shift Register (LFSR). A maximum-period LFSR can be used to generate pseudorandom numbers, as it cycles through 2n-1 combinations before repeating. The all-zeros combination does not appear in this sequence.

solution

1 | module top_module ( |

Lfsr32

See Lfsr5 for explanations.

Build a 32-bit Galois LFSR with taps at bit positions 32, 22, 2, and 1.

Module Declaration

1 | module top_module( |

solution

1 | module top_module( |

Exams/m2014 q4k

question

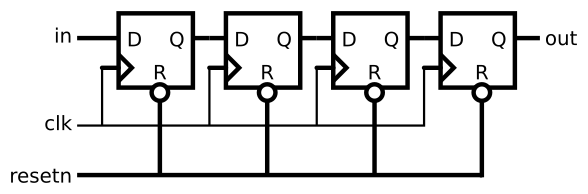

Implement the following circuit:

Module Declaration

1 | module top_module ( |

solution

1 | module top_module ( |

Exams/2014 q4b

question

Consider the n-bit shift register circuit shown below:

Write a top-level Verilog module (named top_module) for the shift register, assuming that n = 4. Instantiate four copies of your MUXDFF subcircuit in your top-level module. Assume that you are going to implement the circuit on the DE2 board.

- Connect the R inputs to the SW switches,

- clk to KEY[0],

- E to KEY[1],

- L to KEY[2], and

- w to KEY[3].

- Connect the outputs to the red lights LEDR[3:0].

(Reuse your MUXDFF from exams/2014_q4a.)

Module Declaration

1 | module top_module ( |

solution

1 | module top_module ( |

Exams/ece241 2013q12

question

In this question, you will design a circuit for an 8x1 memory, where writing to the memory is accomplished by shifting-in bits, and reading is “random access”, as in a typical RAM. You will then use the circuit to realize a 3-input logic function.

First, create an 8-bit shift register with 8 D-type flip-flops. Label the flip-flop outputs from Q[0]…Q[7]. The shift register input should be called S, which feeds the input of Q[0] (MSB is shifted in first). The enable input controls whether to shift. Then, extend the circuit to have 3 additional inputs A,B,C and an output Z. The circuit’s behaviour should be as follows: when ABC is 000, Z=Q[0], when ABC is 001, Z=Q[1], and so on. Your circuit should contain ONLY the 8-bit shift register, and multiplexers. (Aside: this circuit is called a 3-input look-up-table (LUT)).

Module Declaration

1 | module top_module ( |

solution

1 | module top_module ( |

Debug

- 注意case的用法