【Verilog学习】-10-modelsim破解和安装

简单说一下按照该教程就没有问题。

注意:在破解的时候,不能用查找后得到的目录,要在源目录下运行脚本,否者将会失效。

ReferrenceModelSim的安装、破解、使用(缩放算法仿真) - 云+社区 - 腾讯云 (tencent.com)

【CAG_SLAM】-06-AXI

AXI主要参考了一些资料直接进行实践。

Referrence

AXI总线介绍_theboynoName的博客-CSDN博客

从零学习AXI4总线(二):AXI4-Stream 介绍 - 知乎 (zhihu.com)

05AXI4总线axi-stream(AXI4总线实战) - 米联客(milianke) - 博客园 (cnblogs.com)

【大创】-00-BH1750

I2C协议简介

I2C协议

Reference

一文看懂I2C协议 - 知乎 (zhihu.com)

【Verilog学习】-09-时序逻辑-计数器

1 counter16

Build a 4-bit binary counter that counts from 0 through 15, inclusive, with a period of 16. The reset input is synchronous, and should reset the counter to 0.

12345678910111213module top_module ( input clk, input reset, // Synchronous active-high reset output [3:0] q); always @(posedge clk) begin if (reset) begin q <= 0; end else begin q <= q + 1; end end endmodule

2 Counter10

Build a decade counter that co ...

【CNC3018】-00-GetStarted

PCB到G代码

PCB到G代码折腾了两晚上总算是可以用了,进行雕刻机的打板主要需要CAM(Computer Aided Manufacturing)软件和CAD(Computer Aided Design)软件。网络上找到了两款非常好用的软件,应该都是属于这个CAM的范畴,都非常地好用,解决了我的问题。一个是FlatCAM,其作用是将Gerber文件(pcb的eda软件生成的制造文件)转换成G代码(含有雕刻机的刀路等信息的制造文件);第二个是Candle,对gbrl开源雕刻机框架基础上,开发的CNC上位机,可以简易地对CNC进行控制。

Reference

自动编程实现G代码

使用雕刻机雕刻PCB

CandleGetStarted

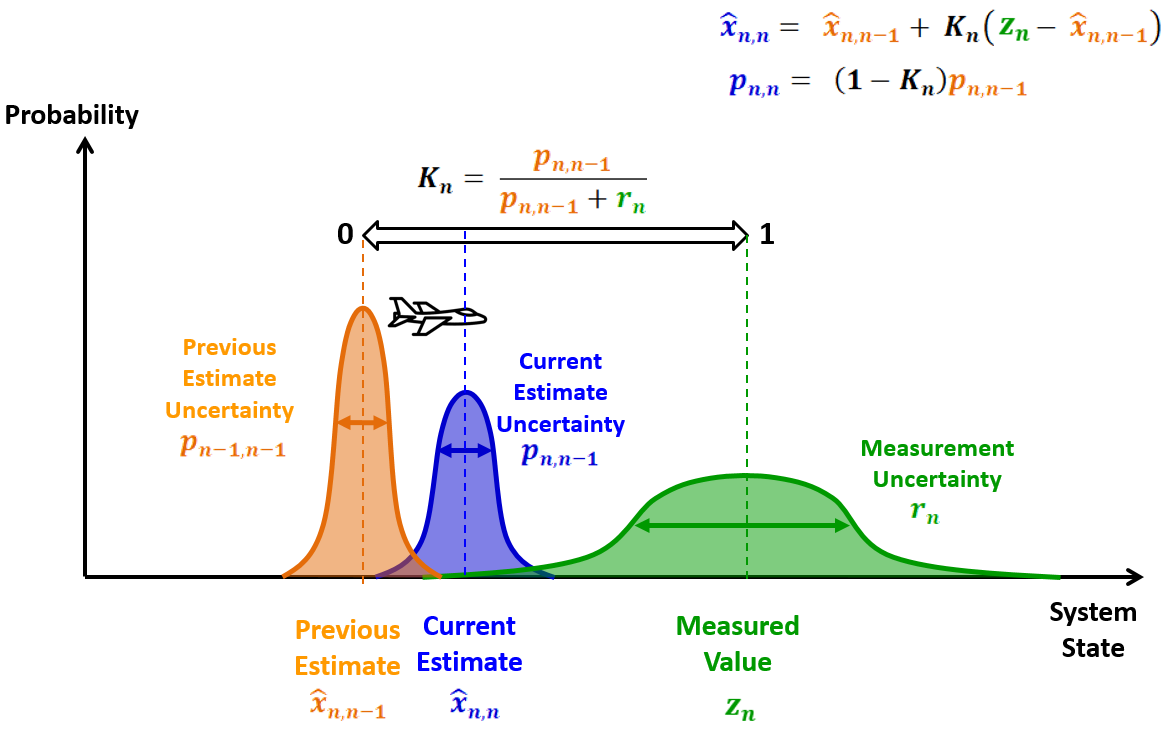

【KalmanFilter】-00-简介

Rudolf Emil Kalman

Rudolf Emil Kálmán[3] (May 19, 1930 – July 2, 2016) was a Hungarian-American electrical engineer, mathematician, and inventor. He is most noted for his co-invention and development of the Kalman filter, a mathematical algorithm that is widely used in signal processing, control systems, and guidance, navigation and control. For this work, U.S. President Barack Obama awarded Kálmán the National Medal of Science on October 7, 2009.[4]

This is quoted from the wikipedia. Kalman wa ...

【CAG_SLAM】-05-Zero-Padding

任务描述

这是padding模块下的一个子模块,负责zero padding的输出。详细功能描述参考前面的【CAG_SLAM】-03-Padding Modules的信息。

端口定义

名称

方向

位宽(bits)

描述

clk

in

1

时钟信号

rst

in

1

reset信号

width

in

12

图片宽度

height

in

12

图片高度

data_i

in

4 x 8

输入数据,原图片数据,每次输入4个字节

fast_busy_i

in

1

fast模块busy标志位信号输入

valid_i

in

1

输入数据有效标志位

data_o

out

4 x 8

输出数据,加上padding之后的数据,每次输出4个字节

pdg_busy_o

out

1

padding模块busy标志位,与valid_i形成握手协议

valid_o

out

1

输出数据有效标志位

实现方案

方案描述同样见【CAG_SLAM】-03-Padding Modules的信息

编程思路首先,输入宽长,第一个数据,停止输入

然后,计算得到cut的数据,开 ...

【CAG_SLAM】-04-除法器

除法器基本思路

对于变量输入的除法中,使用最基础的除法器[^1]。

对于更加具体的除法器的设计可以采用更加灵活的方案:

例如:设计 X / 24 的除法器时,将其分解为 X / 8 * (1 / 4 + 1 / 16 + 1/64 + ···)的形式。,通过加法和移位操作进行处理[^2]。对于其他的被除数,都可以表示为1 / 2 ^ a 的形式进行处理。

跟多的除法器的原理参见一些Stanford的内容[^ 3]。

除法器的实现

关于除法器的设计过程,非常地不顺利,并且第一次设计出来的方案也并不好。这主要是由于读别人的代码少了,输入不够,导致自己的输出并没能达到老师的要求。最后,通过查阅StackOverflow等网站的文章,勉强搞定了设计。这里简单总结一下经验教训:

思考要谨慎,不要因为一时的得失而忘形或失意。

做事之前一定要有相关的输入,借鉴和思考别人的经验

时间安排要合理一些

最后方案

A / 24 = A / 8 / 3 = A / 8 * (1 &#x ...

【Verilog学习】-08-时序逻辑-基础触发器

1.DFF

Create a single D flip-flop.

12345678module top_module ( input clk, // Clocks are used in sequential circuits input d, output reg q ); always @(posedge clk) begin q <= d; endendmodule

2.DFF8

Create 8 D flip-flops. All DFFs should be triggered by the positive edge of clk.

123456789module top_module ( input clk, input [7:0] d, output [7:0] q); always @(posedge clk) begin q[7:0] <= d[7:0]; // q <= d; endendmodule

3.Dff8r

Create 8 ...

【vivado】-00-install

前言这里开始终于着手把落下的工作开始真正一步一步地落实下去了,这两天的心情比较低落,主要是前期对自己的要求没有达到目标,导致现在的进展非常地缓慢。对科研和学习一定要高标准、严要求,没有什么是做不了的,大多数的问题都可以靠时间解决。一定要把时间安排妥当。

下载

下载地址:Downloads (xilinx.com)

安装

安装时,可按照步骤选取自己需要的版本,这里选取的是WebPackage版本。

具体可以参考最后一个教程。

使用

界面中的右边的导航栏表明了所有的流程,按照此流程进行操作。这里主要说明编写好一个v文件之后,如何进行仿真和综合。

参考资料

Vivado安装和使用 | 教程 (ustc.edu.cn)

Vivado的下载和安装_核小体的博客-CSDN博客_vivado下载

数字 IC 技能拓展(29)Xilinx_Vivado_SDK_2019.1 安装详细教程_新芯时代的博客-CSDN博客_vivado2019安装(这一个链接包括激活的license)

Vivado下的仿真入门_leon_zeng0的博客-CSDN博客_vivado仿真