【RPI】-00-Hello-Pi

安装系统镜像安装RPI的镜像非常的顺畅,在完成安装后,主要遇到的问题是板载的wifi坏掉了(wifi模块表面肉眼可见有一个坑)。上次买台式机送了一个MW150UH的网卡,想着安装上去,没有找到wifi驱动,导致这两天的进度非常缓慢。

现在的解决办法是买一个免驱wifi模块的试一下。

HelloPi在树莓派上打印了一个HelloWorld,啥也不是。

遇见的问题:

Ubuntu上有线网连接不上树莓派,暂时不清楚原因(报错是:activation of network connection failed)终于连上了,根据这位大佬的博客(树莓派网线直连Ubuntu_栋次大次的博客-CSDN博客),更改了一下有线网络的设置:

解决了一个小问题:刚刚不能google,以为是下午为了连树莓派装了arp-scan的原因;最后反应过来是下午调系统设置的network的时候不小心动了一下Network Proxy的设置导致的(设置成手动模式):

Linux开发环境搭建为树莓派分配固定的IP地址重启之后,通过网络设置找到本机ip:

然后通过nmap命令找到树莓派的地址,最后连接成功进入树莓派 ...

【xup_summer_camp】-05-hls学习(下)

B站课程学习

24课:案例分析_哔哩哔哩_bilibili

一共25节课程,比较精简。主要讲HLS基本使用中关于变量类型、数组和函数等基础,同时重点讲了各种Directive的使用(有利于实现不同的设计指标等)。

目前已经看到24课,前面笔记记录在笔记本上,第24课讲了一个具体的HLS工程实例,此次笔记主要记录一下实现过程。

Cordic算法实现算法原理cordic算法是一种通过简单运算(加、减、移位、查找表)进行迭代(旋转)实现复杂函数计算(三角函数、乘除法、双曲函数等)的算法,适用于没有浮点运算的系统(微控制器、FPGA等)。

CORDIC - Wikipedia

CORDIC (for COordinate Rotation DIgital Computer), also known as Volder’s algorithm, or: Digit-by-digit method Circular CORDIC (Jack E. Volder), Linear CORDIC, Hyperbolic CORDIC (John Stephen Walther), and Ge ...

【Verilog学习】-13-四个应用大题

搞了一下午博客环境我也是醉了

Cs450/timerQuestionImplement a timer that counts down for a given number of clock cycles, then asserts a signal to indicate that the given duration has elapsed. A good way to implement this is with a down-counter that asserts an output signal when the count becomes 0.

At each clock cycle:

If load = 1, load the internal counter with the 10-bit data, the number of clock cycles the timer should count before timing out. The counter can be loaded at any time, including when ...

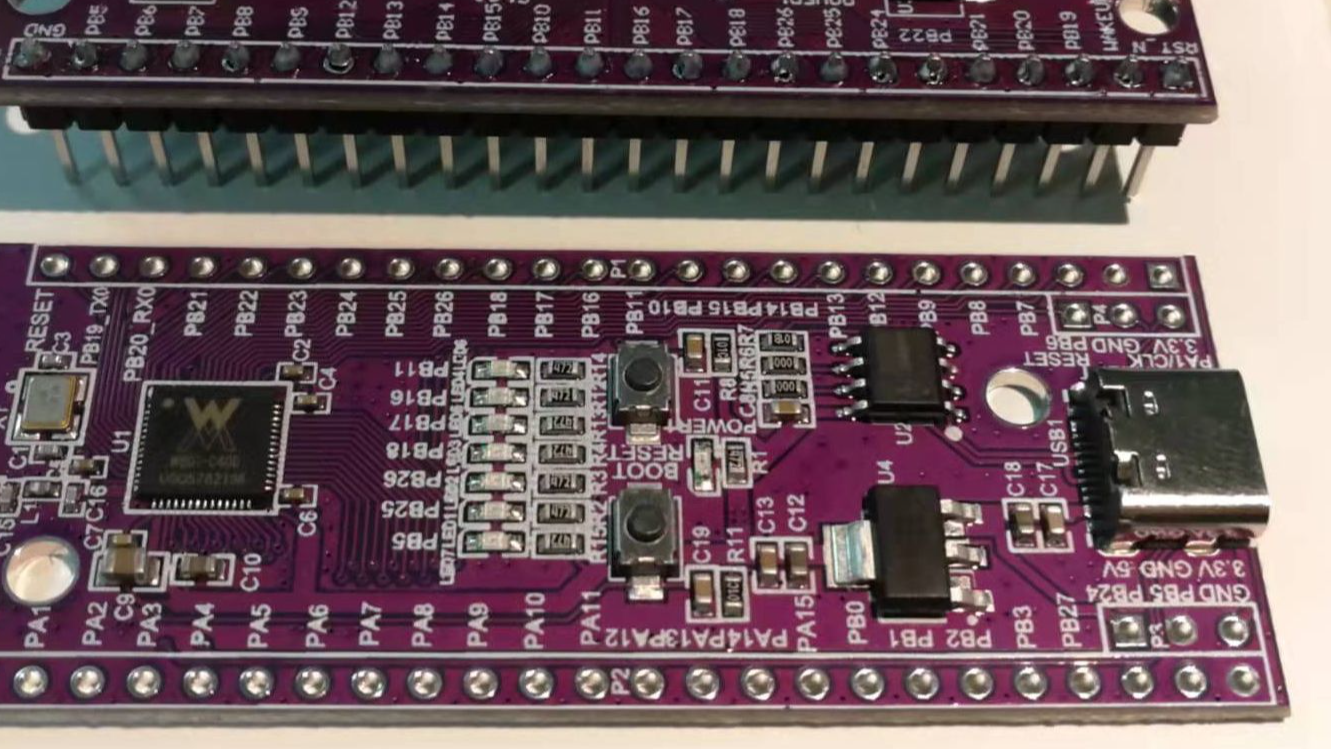

【HLK-W801】-01-OLED显示

实现思路将官方给的例程移值到这个小开发板上即可。

使用SPI通信协议(使用GPIO模拟SPI),注意移植的时候看一下源代码,需要注意改一下底层的IO操作代码即可。

实现过程复习一下SPI通信协议SPI工作有四种模式,这里以最常见的CPOL(时钟极性) = 0,CPHA (时钟相位)= 0,进行讨论。

SPI Block Guide V4 (nxp.com)

注意看红色框出的地方,是我们考虑的情况:当出现上升沿的时候进行采样。因此,传输的方式应该是,先改变数据,再出现时钟上升沿。然后,延时再改变时钟为下降沿,进入限一个周期。同时注意,片选信号要保持为低电平。

看源代码原代码就是用的模拟SPI(软件实现的)。

再源代码基础上改变了IO操作的宏定义,暂时没有移植成功。

已经尝试过排查的问题:

IO软件功能正常,通过软件改写IO,并读取IO值,比对成功。没有万用表,引脚电平可能存在问题。

SPI频率排查,在上升沿后加入过1us延迟,初始化过程明显变慢,但是依旧没有反应。

可能有问题的地方:

估计代码没有问题,出现问题大概率在模块上面,供电还未检查。也可能是模块自身的 ...

【札记】HowToLive

如何去生活?我一直在寻找这个问题的答案,现在又一次迷失了方向。我总是在问别人这个问题,总是想通过别人的生活来找到这个问题的答案。

学习出现了困难,就去找别人的学习方法;健身遇到了瓶颈,就去模仿别人的训练计划。

刚开始,这样做是没有问题的,毕竟innovation都是在imitation的基础上的,但是问题就是在于已经完成了immitation之后。没有再去innovation和rethink这些,继而遇到问题之后,继续immitation。但是问题的关键已经不再是有没有,而是好不好、适合不适合。此后,更多的immiation只会带来更多的困惑而不再是breakthrough。

我想,在生活这个大问题上,继续向外寻找答案,可能已经不再适用了。我应该静下心来,问问自己。

我现在处于哪一个人生阶段经过了大二、大三这两年,我已经基本上完成了所谓一心专研书本知识、打下坚实基础的本科阶段了。这两年确实是基本上都沉浸在了专业课和自己今后想要从事的方向的学习上了,总的来说,埋头拉车大于抬头看路。期间经历了一些精神压力和迷茫的人生状态,但是,我还是推着自己毫不停息的继续向前,我总是瞄着这个时间点(也就是 ...

【HLK-W801】-00-跑马灯

搞到一块W801小开发板来耍耍(基于平头哥的内核,用的是自研指令集C-SKY)。资料有点少,今天先看看官方的sdk里面有什么东西可以用。

通过官方给的demo包,改了一下GPIO的demo就可以用了。wm-sdk-w80x: Original Winner Micro SDK for W801 (gitee.com)

参考资料

单片机—HLK-W801开发环境搭建_胖哥王老师的博客-CSDN博客

【Verilog学习】-12-verification

Bugs mux2QuestionThis 8-bit wide 2-to-1 multiplexer doesn’t work. Fix the bug(s).

Module Declaration12345module top_module ( input sel, input [7:0] a, input [7:0] b, output [7:0] out );

Solution123456789101112131415161718192021/**module top_module ( input sel, input [7:0] a, input [7:0] b, output out ); assign out = (~sel & a) | (sel & b);endmodule**/module top_module ( input sel, input [7:0] a, input [7:0] b, output [7:0] out ); assign out = ...

【蜂鸟E203】-00-初识CPU设计

蜂鸟的RTL代码风格

模块化的风格:定义一些基本的带有参数化的模块,并进行模块的例化来搭建整个数字电路。

当是并行优先级选择的时候,使用assign语句代替if - else语句,前者能够传播不定态,且能透过组合逻辑实现并行的优先级选择。

断言:用来Debug,具体使用后面再看。

数据通路上的寄存器可不用带reset,控制通路上的寄存器需要带reset。

clk和rst只能接入寄存器而禁止用于其他任何逻辑功能。

看到后面了2022-10-09:

看了10、11和12章。

其中10章讲写回的机制,看的有点不明所以,可能是前面看了太久忘记讲什么东西了。简单来说就是讲了往存储器里面写回东西的模块。

11章在讲存储器结构,同时用了哈佛和冯诺依曼的储存思想。

12章讲总线,axi、ahb、apb一个个熟悉的名字出现了,蜂鸟使用了结合前两个总线机制的icb协议。

中断机制今天看到完了中断和异常的相关内容,RISC-V架构对于它的处理是采用了简洁有效的办法,没有硬件嵌套机制,要实现中断的嵌套需要从软件上进行寄存器的配置操作。

总的来说,中断机制是处理器设计中,最为繁琐的一个部分之一。及时采用了简化 ...

【xup_summer_camp】-04-hls学习(上)

本博客为Xilinx HLS课程笔记

FPGA的单元逻辑单元基本的逻辑功能、加法功能(或者使用DSP48)

算术逻辑单元DSP48

存储单元Block RAM(大块数据存储)、LUT in SLICEM(小容量 ≤ 1kb)

数组和BRAM之间进行映射

本课程关注点是:如何写高效率的HLS代码(C/C++)

HLS的机制硬件设计的重点和难点:时序和并行性分析。

C/C++关注算法本身。

C → HDL 流程Scheduling(调度) → Control Logic Extration(控制逻辑提取) → Binding(硬件映射)

简单,无控制逻辑的例子:

涉及到循环(有状态机),加入控制逻辑的例子:

HLS 通过状态机来控制算法的进程。

【xup_summer_camp】-03-Sobel算子的FPGA实现

跑文档IP的问题出问题了HLS生成的IP是空的,有一点小烦,不知道哪里有毛病。

现在目测是创建工程的时候,由于选择的顶层文件不正确导致的。

发现一个问题,没有按照文档选择正确的器件(创建hls工程的时候):

改过来后,出现IP,正常了。

BlockDesign的问题开始连线不正确,AutoConnection有一个模块没有出现,检查后发现是忘记给ZYNQ Processing的IP进行配置了。

给ZYNQ加上这一个AXI端口后,正常。

顺利跑下来了,中间没什么事故。接下来就是进一步进行HLS的开发而不是仅仅用这个python来跑程序了。